Author:netwing Time:2024-04-23 Number Of Views:

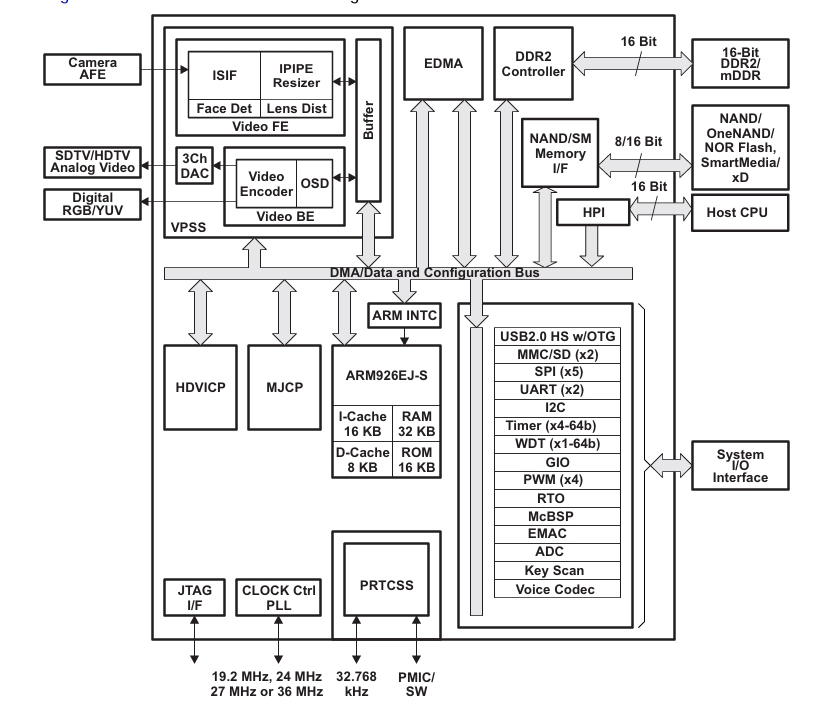

TMS320DM368ZCED - High Performance Digital Media System on Chip (DMSoC) -432MHz ARM926EJ-S Clock Rate - Dual Video Image Coprocessor (HDVICP, MJCP) Engine - Supports a Range of Encoding, Decoding, and Video Quality Operations - Video Processing Subsystem - HWFaceDetect Engine - Adjusts Engine Size from 1/16x to 8x • 16 bit Parallel AFE (Analog Front End) Interface, Frequency Up to 120 MHz • 4:2:2 (8/16 bit) Interface • 8/16 bit YCC and Up to 24 bit RGB888 Digital Output • 3DAC for HDAnalog Video Output • Hardware Screen Display OSD) - capable of 1080p 30fps H.264 video processing - peripherals including EMAC USB 2.0 OTG, DDR2/NAND, 5 SPI, 2 UART, 2 MMC/SD/SDIO, key scan -8 different boot modes and configurable power-saving modes - compatible with DM365 pin to pin and software - provides extended temperature (-40 º C -85 º C) -3.3V and 1.8V I/O, 1.35V core -338 pin ball gate array using 65nm process technology - High performance digital media on chip system (DMSoC) -432MHz ARM926EJ-S clock rate -4:2:2 (8/16 bit) interface - supports 1080p 30fps H.264 video Processing - compatible with DM365 processor pins - compatible with ARM9 ™ Fully software compatible - provides extended temperature for 432MHz 1 device • ARM926EJ-S ™ Kernel - Supports 32-bit and 16 bit (thumb) ® Mode Instruction Set - DSP Instruction Extension and Single Cycle MAC - ARM ® Jazelle ® Technology - Embedded ICE-RT Logic for Real time Debugging • ARM9 Memory Architecture -16K Byte Instruction Cache -8K Byte Data Cache -32K Byte RAM -16K Byte ROM - Small End • Dual Video Image Coprocessor (HDVICP, MJCP) Engine - Supports a Series of Encoding and Decoding Operations - H.264 MPEG4, MPEG2, MJPEG, JPEG, WMV9/VC1 • Video processing subsystem - Front end provided: • HWFaceDetect engine • Hardware IPIPE for real-time image processing - Adjust engine size - Adjust image size from 1/16x to 8x - Independent horizontal/vertical control - Two synchronous output paths • IPIPE interface (IPIPEIF) • Image sensor interface (ISIF) and CMOS imager interface • 16 bit parallel AFE (analog front end) interface up to 120 MHz • Seamless interface with regular video decoder • BT.601/BT.656/BT.1120 digital YCbCr 4:2:2 (8/16 bit) Interface • Histogram module • Lens distortion correction module (LDC) - Backend provides: • Hardware screen display (OSD) • Composite NTSC/PAL Video Encoder Output • 8/16 bit YCC and up to 24 bit RGB888 Digital Output • 3DAC for HDAnalog Video Output • LCD Controller • BT.601/BT.656 Digital YCbCr 4:2:2 (8/16 bit) Interface • Analog to Digital Converter (ADC) • Power Management and Real Time Clock Subsystem (PRTCSS) - Real Time Clock • 16 bit Host Port Interface (HPI) • 10/100 Mb/s Ethernet Media Access Controller (EMAC) - Digital Media - Compliant with IEEE 802.3 Standard - Supports Media Independent Interface (MII) - Manage Data I/O (MDIO) Module • Key Scan • Voice Encoding and Decoding Device • External Memory Interface (EMIF) - DDR2 and mDDRDDRAM16 bit wide EMIF with 256 MB address space (1.8V I/O) - Asynchronous 16/8 bit wide EMIF (AEMIF) • Flash interface - NAND (8/16 bit wide data) -16MB NORFlash SRAM - OneNAND (16 bit wide data) • Flash card interface - Two Multimedia Card (MMC)/Secure Digital (SD/SDIO) - SmartMedia/xD • Enhanced Direct Memory Access (EDMA) controller (64 independent channels) • USBPort integrates 2.0 high-speed PHY, supports - USB2.0 high-speed device - USB2.0 high-speed host (mini host, supports one external device) - USBonTheGo (HS USB OTG) • 4 64 bit universal timers (each configurable as 2 32-bit timers) • 1 64 bit watchdog timer • 2 UARTs (1 with RTS and CTS) Fast UART for flow control • 5 serial port interfaces (SPI) with two chip options per interface • 1 master/slave internal integrated circuit (I2C) bus ™ • A multi-channel buffered serial port (McBSP) - I2S - AC97 audio codec interface - via software's S/PDIF - standard speech codec interface (AIC12) - SPI protocol (main mode only) - direct interface with T1/E1 framers - time division multiplexing mode (TDM) -128 channel mode -4 pulse width modulator (PWM) outputs -4 RTO (real-time output) outputs - up to 104 general-purpose I/O (GPIO) pins (multiplexed with other device functions) - boot mode - on-chip ARM ROM bootloader (RBL) from NAND flash MMC/SD, UART, USB, SPI, EMAC or HPI - AEMIF (NOR and OneNAND) startup • configurable power-saving mode • crystal oscillator or external clock input (usually 19.2 MHz, 24 MHz, 27 MHz or 36 MHz) • flexible PLL clock generator • debugging interface support - IEEE-1149.1 (JTAG) ™ Boundary Scan Compatibility - ETB (Embedded Tracking Buffer) with 4K bytes of tracking buffer memory - Device Revision ID can be read by ARM • 338 pin Ball Grid Array (BGA) package (ZCE suffix), 0.65mm ball pitch • 65nm process technology • 3.3V and 1.8V I/O, 1.35V internal • Community resources

Developers can now provide clear multi format videos up to 1080p H.264 at 30fps (encoding and closed-loop decoding) in digital video design without worrying about video format support, limited network bandwidth, limited system storage capacity, or cost issues, without worrying about using Texas Instruments (TI)'s new TMS320DM368 DaVinci ™ Video processor. DM368 can achieve high-definition video processing of 1080p 30fps H.264, and is fully pin compatible with the DM365 processor. It uses the same ARM926EJ-S core and runs at a frequency of 432 MHz. This ARM9 based DM368 device supports H.264BP/MP/HP, MPEG-4, MPEG-2, MJPEG, and VC1/WMV9 codecs that meet production standards, allowing customers to flexibly choose the appropriate video codec for their applications. These codecs run on independent co processors (HDVICP and MJCP), offloading all compression requirements from the main ARM kernel. This enables developers to obtain the best performance from ARM that meets their application requirements, including their multi-channel, multi stream, and multi format requirements. Video surveillance designers have achieved higher compression efficiency to provide more storage space without causing network bandwidth constraints. Developers of media playback and camera driven applications such as visual doorbells, digital signage, digital recorders, portable media players, etc. can leverage the advantages of low power consumption and ensure interoperability and product scalability by leveraging the full range of codecs supported on the DM368. In addition to multi format high-definition videos, the DM368 also comes with a set of peripherals that can save developers system costs and complexity, thereby achieving seamless interfaces with most additional external devices required for video applications. The image sensor interface is flexible enough to support CCD, CMOS, and various other interfaces, such as BT.656 and BT1120. DM368 also provides high integration with high-definition display support, including three built-in 10 bit high-definition analog video to analog converters (DACs), DDR2/mDDR, Ethernet MAC, USB 2.0, integrated audio, host port interface (HPI), analog-to-digital converters, and more functions, saving developers overall system costs and space on the circuit board, thus achieving a thinner and more fashionable design.

Previous Article:TLC2252CPWR

Next Article:AM26LS31CDR

Contact Us:0755-82760106

Contact Us:0755-82760106

Proposal:0755-83260671

Proposal:0755-83260671

Mailbox:jessie@ruizhengwei.com

Mailbox:jessie@ruizhengwei.com

Address:18F, Building A, Rongde International, Henggang Street, Longgang District, Shenzhen City, Guangdong Province

Address:18F, Building A, Rongde International, Henggang Street, Longgang District, Shenzhen City, Guangdong Province

Skype

Copyright © 2024 Shenzhen Ruizheng Microelectronics Co., Ltd Copyright Record number: Yue ICP Bei 2024178191-1 Background Login